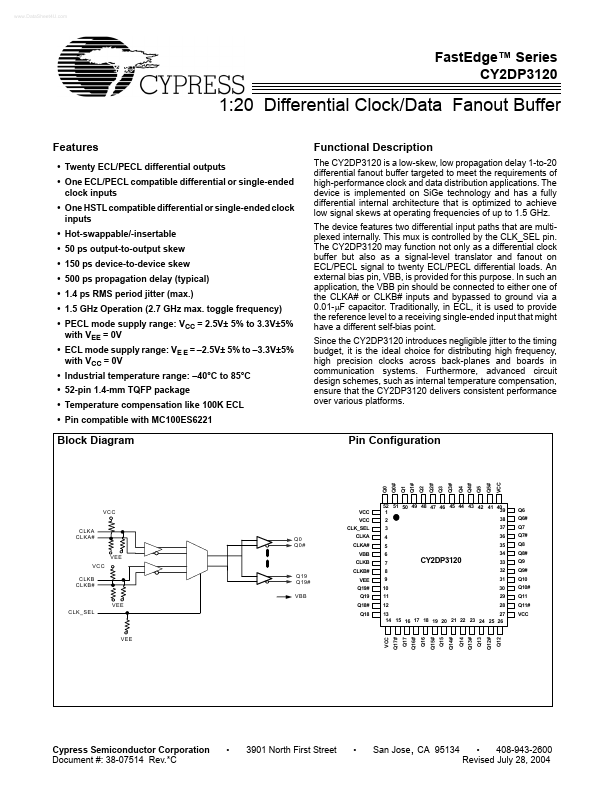

CY2DP3120 Overview

Key Features

- Twenty ECL/PECL differential outputs

- One ECL/PECL compatible differential or single-ended clock inputs

- One HSTL compatible differential or single-ended clock inputs

- Hot-swappable/-insertable

- 50 ps output-to-output skew

- 150 ps device-to-device skew

- 500 ps propagation delay (typical)

- 1.4 ps RMS period jitter (max.)

- 1.5 GHz Operation (2.7 GHz max. toggle frequency)

- PECL mode supply range: VCC = 2.5V± 5% to 3.3V±5% with VEE = 0V